MIPS

(

англ.

Microprocessor without Interlocked Pipeline Stages

[1]

) ? арх?тектура м?кропроцесор?в, розроблена компан??ю MIPS Computer Systems (нин? MIPS Technologies) в?дпов?дно до концепц?? проектування процесор?в

RISC

, тобто концепц?? з? скороченим набором команд. Ранн? модел? процесора мали

32-б?тну

структуру, п?зн?ше з'явилася

64-б?тна

верс?я. ?сну? багато модиф?кац?й ц??? арх?тектури, включаючи MIPS I, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS32 (для 32-б?тно? реал?зац??) ? MIPS64 (для 64-б?тно? реал?зац??). MIPS32 ? MIPS64 визначають як наб?р рег?стр?в керування, так ? наб?р команд. Арх?тектура MIPS з порядком байт

little endian

назива?ться mipsel.

[2]

Кр?м цього, доступн? доповнен? модел?, наприклад:

- MIPS-3D

? включа? в себе наб?р

SIMD

команд для обробки

чисел з рухомою комою

, призначений для вир?шення простих

3D

завдань;

- MDMX

(MaDMaX) ? з ?ще ширшими можливостями, ма? наб?р SIMD команд та команд з використанням 64-б?тових рег?стр?в з рухомою комою для роботи з ц?лими числами

[

що?

]

;

- MIPS16e

? стиска? пот?к команд для зменшення обсягу зайнято? програмами пам'ят?;

- MIPS MT

(Multi-Threading) ? забезпечу?

багатопотоковий

режим оброблення.

Арх?тектуру MIPS часто вивчають в програм? курсу ≪Комп'ютерна арх?тектура≫ в ун?верситетах ? техн?чних л?цеях. Ця арх?тектура мала ?стотний вплив на подальший розвиток ?нших процесор?в RISC-арх?тектури, зокрема на

Alpha

.

Р?зн? реал?зац?? MIPS використовуються в основному у

вбудованих системах

, наприклад, в пристроях

Windows CE

,

маршрутизаторах

,

шлюзах

, а також в ?грових консолях, таких як

Sony PlayStation

2 ?

Sony PlayStation Portable

. До к?нця 2006 року вони застосовувалися ? в комп'ютерах

SGI

. До к?нця 1980-х ? 1990-х ця арх?тектура широко використовувалася багатьма компан?ями, серед них

Digital Equipment Corporation

,

NEC

, Pyramid Technology,

Siemens Nixdorf

? Tandem Computers. З середини до к?нця 1990-х рок?в кожним трет?м м?кропроцесором на ринку виробництва був процесор арх?тектури MIPS.

Основоположник RISC

[

ред.

|

ред. код

]

У

1981

роц? колектив п?д кер?вництвом

Джона Геннес?

з

Ун?верситету Стенфорда

почав роботу над проектом, який отримав назву MIPS. Головною ?де?ю було зб?льшити продуктивн?сть процесора, використовуючи подовжений

конве?р

. Концепц?я застосування конве?ра як основно? технолог?? була в?дома ще задовго до цього (наприклад, в

IBM

801), але вона не використовувала весь св?й потенц?ал.

Центральний процесор

включа? в себе к?лька спец?альних субблок?в, таких як декодери команд, ц?лочисельний

АЛП

(арифметико-лог?чний пристр?й), блоки завантаження / збер?гання (робота з пам'яттю) ? т. д. В традиц?йн?й не оптим?зован?й реал?зац?? окрема команда в програм? ма? бути (майже завжди) завершена, перш н?ж запуститься ?нша; в той час як в конве?рн?й арх?тектур? посл?довн? команди можуть виконуватися паралельно. Наприклад, коли математична ?нструкц?я вноситься в блок з рухомою комою, блок завантаження / збер?гання пам'ят? може в цей же момент викликати наступну команду.

Одн??ю з головних перешкод у використанн? конве?ра був той факт, що деяк? команди, так? як д?лення, виконуються набагато довше за ?нш?. Внасл?док цього центральному процесору доводиться чекати, перш н?ж передати на конве?р наступну команду. ?дине вир?шення ц??? проблеми ? використовувати сер?ю блокувань, що дозволяють певним стад?ям конве?ра сигнал?зувати, що вони зайнят?. В цьому випадку виконання наступних команд потоку призупиня?ться. Група Геннес? розглядала ц? блокування як величезний бар'?р у зб?льшенн? продуктивност?, оск?льки було необх?дно звертатися до вс?х модул?в центрального процесора, що займа? зайвий час ? обмежу? тактову частоту. Головним завданням розробки пристро?в MIPS було вкласти кожну п?дфазу кожно? команди, в тому числ? кешування, в один цикл, таким чином уникаючи необх?дност? в блокуваннях.

Хоча така реал?зац?я ? виключала б деяк? дуже корисн? операц??, так? як множення ? д?лення, очевидно, що гранична продуктивн?сть системи значно зб?льшилася б, бо м?кросхеми змогли б працювати з вищою тактовою частотою. Досягнення високо? швидкост? з використанням блокувань було б складним, тому що час, необх?дний для встановлення блокувань, пропорц?йний тактов?й частот? (залежн?й, в свою чергу, в?д розм?ру кристала). Ось чому виключення вищезазначених операц?й стало сп?рним питанням.

?нша в?дм?нн?сть дизайну MIPS в?д конкуруючих з ним Berkeley-арх?тектур ? це впроваджена в Berkeley-

RISC

можлив?сть обробки виклику п?дпрограм. Щоб зб?льшити продуктивн?сть наст?льки загально? задач?, в Berkeley-RISC була використана технолог?я, яка назива?ться рег?стровим в?кном, яка, тим не менш, обмежувала максимальну глибину багатор?вневих виклик?в. Кожен виклик п?дпрограми вимагав свого набору рег?стр?в, що призводило до необх?дност? зб?льшення ?х к?лькост?. А апаратна реал?зац?я даного механ?зму займала додатковий прост?р в кристал? ЦП. Але Геннесс? вважав, що ≪ретельн?ший≫ комп?лятор м?г би знайти в?льн? рег?стри для передач? параметр?в функц??, ? що всього лише зб?льшення числа рег?стр?в могло б не т?льки спростити цю задачу, але ? зб?льшити продуктивн?сть вс?х операц?й. Тому було прийнято р?шення в?дмовитися в?д дано? технолог?? в MIPS.

Арх?тектура MIPS була, в деякому в?дношенн?, найтипов?шою для

RISC

. Щоб заощадити б?ти в код? команди, в RISC було зменшено к?льк?сть ?нструкц?й для кодування. В MIPS з 32 б?т?в слова всього 6 використовуються для основного коду, а ?нш? можуть м?стити або ?дину 26-б?тну адресу переходу, або до 5 пол?в, що встановлюють в?д 1 до 3 рег?стр?в + величина зсуву рег?стра. ?сну? ? ряд ?нших формат?в, наприклад, коли 2 рег?стри задаються безпосередньо вид?леним 16-б?товим полем ? так дал?. Такий розпод?л дозволив процесору завантажувати команду ? необх?дн? ?й дан? в одному цикл?, в той час як у стар?ших арх?тектурах (що не були

RISC

), наприклад,

MOS Technology 6502

, були потр?бн? окрем? цикли для завантаження основного коду ? даних.

Це було одним з головних удосконалень продуктивност?, як? пропонували RISC. Однак, варто сказати, що не RISC арх?тектури все ж досягли под?бно? швидкост?, але ?ншими засобами (такими, як черги в ЦП).

Перша апаратна реал?зац?я

[

ред.

|

ред. код

]

У 1984 роц?, переконаний у комерц?йному усп?ху сво?? розробки, Геннесс? покинув Стенфорд, щоб заснувати компан?ю MIPS Computer Systems. У 1985 роц? була реал?зована перша верс?я м?кропроцесора MIPS ? R2000, допрацьована в 1988 роц? ? отримала назву R3000. Ц? 32-б?тов? процесори лягли в основу компан?? в 1980-х ? використовувалися переважно в SG-сер?ях робочих станц?й. Нов? комерц?йн? проекти не в?дпов?дали Стенфордським науковим досл?дженням, так як практично вс? блокування виконувалися на апаратному р?вн?, до того ж операц?? множення ? д?лення були повн?стю реал?зован?.

У 1991 роц? MIPS вперше був представлений як 64-б?тний м?кропроцесор, у верс?? R4000. R4000 ма? розширений

TLB

, в якому запис м?стить не лише в?ртуальний адресу, але ? в?ртуальний ?дентиф?катор адресного простору. Такий буфер усува? основн? проблеми продуктивност? м?кроядра, досить пов?льного в арх?тектурах конкуруючих компан?й (

Pentium

,

PowerPC

,

Alpha

) через необх?дн?сть скидати TLB п?д час частого перемикання контексту.

Тим не менш, у MIPS виникали ф?нансов? труднощ? у зв'язку з поставкою процесор?в на ринок. Проект був наст?льки важливий для

SGI

(в той час були одними з небагатьох основних покупц?в MIPS), що в 1992 роц?

SGI

викупили права на компан?ю з умовою гарант??, що конструкц?я м?кропроцесор?в не зм?ниться. Ставши доч?рньо? компан??ю, MIPS Computer Systems отримали назву MIPS Technologies.

Л?цензована арх?тектура

[

ред.

|

ред. код

]

На початку 1990 року MIPS почали л?цензування сво?х розробок для сторонн?х постачальник?в.

?дея виявилася усп?шною через простоту ядра, яке знаходило безл?ч застосувань, де ран?ше використовувалися набагато менш ефективн?

CISC

-арх?тектури, з т??ю ж к?льк?стю ? т??? ж ц?ною схем (2 цих критер?ю т?сно пов'язан?: ц?на ЦП, як правило, залежить в?д к?лькост? схем ? контакт?в). Компан?я

Sun Microsystems

зробила аналог?чну спробу л?цензування ядра

SPARC

, але ?х х?д не мав под?бного усп?ху. До к?нця 1990-х MIPS стали найважлив?шою компан??ю у виробництв? вбудованих процесор?в, ? в 1997 роц? 48-м?льйонн? поставки процесор?в на баз? MIPS змусили RISC-арх?тектури вит?снити популярне с?мейство процесор?в 68k. MIPS були наст?льки усп?шними, що в 1998 роц? SGI передали частину актив?в MIPS Technologies. На сьогодн? половина доход?в MIPS надходить з л?цензування розробок, а велика частина ?ншо? половини ? з контракт?в на розробку ядер для виробництва сторонн?ми постачальниками.

У 1999 роц? MIPS формал?зували сво? системи л?цензування навколо двох основних конструкц?й ? 32-розрядно? 'MIPS32 (на баз? MIPS II з деякими додатковими функц?ями MIPS III, IV MIPS ? MIPS V) ? 64-розрядних MIPS64' (на баз? MIPS V). Л?ценз?я на MIPS64 була придбана кожно? з компан?й

NEC

,

Toshiba

? SiByte (згодом придбана Broadcom) в?дразу ж п?сля оголошення про ?? випуску. Незабаром, до них при?дналися

Philips

, LSI Logic ? IDT. Усп?х випливав за усп?хом, ? сьогодн? процесори MIPS ? одним з найб?льш затребуваних товар?в на ринку пристро?в комп'ютерного типу (кишенькових комп'ютер?в, приставок тощо), поряд з ?ншими розробниками, марно намагаються ?х вит?снити.

Через к?лька рок?в п?сля того, як MIPS-арх?тектура стала л?цензовано?, вона почала привертати все б?льше ? б?льше нових компан?й з розробки процесор?в. Першою такою компан??ю була Quantum Effect Devices (див. наступний розд?л). Команда розробник?в, що з?брали MIPS R4300i заснувала компан?ю SandCraft, яка надала компан?? NEC новий процесор R5432, а трохи п?зн?ше змодельовану R71000 ? один з перших нестандартних процесор?в для ринку вбудованих систем. Команда засновник?в компан?? DEC

StrongARM

зрештою розд?лилася на дв? нов? компан?? з розробки процесор?в, в основу яких л?г MIPS: SiByte, яка виробляла SB-1250 ? одну з перших чипових систем з високою продуктивн?стю, заснованих на MIPS (

SOC

) ? Alchemy Semiconductor (п?зн?ше придбана AMD), яка виробляла Au-1000 SOC для малопотужних додатк?в. Компан?я Lexra використовувала арх?тектуру, под?бну MIPS, додавши до не? DSP для ринку ауд?о м?кросхем, а також п?дтримку багатопотокового режиму для мережевого ринку. Так як Lexra не купувала л?ценз?ю на MIPS, незабаром, м?ж двома компан?ями розгор?лися судов? процеси. Перший був досить швидко погашений вже п?сля того, як Lexra пооб?цяла не просувати сво? процесори, як под?бн? з MIPS. Другий процес (про патент MIPS 4814976 на обробку невир?вняного ?нструкц?? (unaligned) доступу до пам'ят?) був б?льш затяжним ? негативно позначилася на б?знес? обох компан?й, а по його завершенн? MIPS Technologies видали Lexra безкоштовну л?ценз?ю та виплатили грошову компенсац?ю в крупному розм?р?.

Сл?дом за цими под?ями на ринку з'явилися дв? компан??, що спец?ал?зуються на створенн? багатоядерних пристро?в, що використовують арх?тектуру MIPS. Корпорац?я Raza Microelectronics викупили виробничу л?н?ю у менш усп?шних SandCraft, а пот?м почали випускати восьмиядерн? пристро? для ринку телекомун?кац?й ? мереж. Cavium Networks, спочатку були постачальником засоб?в захисту процесор?в, теж почали виробництво восьми, а п?зн?ше ? 32-ядерних арх?тектур для тих же ринк?в. Обидв? компан?? сам? проектували ядра, ? лише л?цензували розробки, зам?сть того, щоб купувати готов? процесори MIPS.

Серед виробник?в, як? створили робоч? станц?? з використанням м?кропроцесор?в MIPS так? компан??, як

SGI

, MIPS Computer Systems, Inc., Whitechapel Workstations, Olivetti, Siemens-Nixdorf, Acer, Digital Equipment Corporation, NEC, ? DeskStation. У числ? операц?йних систем, перенесених на арх?тектуру MIPS: IRIX компан?? SGI,

Windows NT

(до верс?? 4.0) компан??

Microsoft

,

Windows CE

,

Linux

,

BSD

,

UNIX

System V, SINIX,

QNX

, ? операц?йна система RISC безпосередньо належить компан?? MIPS Computer Systems.

На початку 1990-х ?снувало припущення, що MIPS разом з ?ншими потужними процесорами RISC незабаром обженуть арх?тектуру IA32 компан??

Intel

. Цьому сприяла п?дтримка двох перших верс?й

Windows NT

для

Alpha

, MIPS ? PowerPC компан??

Microsoft

, ?, дещо меншою м?рою, ? арх?тектури Clipper ? SPARC. Однак, як т?льки Intel випустив нов?тн? верс?? ЦП класу

Pentium

, Microsoft Windows NT v4.0 перестав п?дтримувати все, кр?м

Alpha

? Intel. П?сля р?шення SGI перейти на арх?тектури

Itanium

?

IA32

, процесори MIPS практично повн?стю перестали використовуватися в персональних комп'ютерах.

Ринок вбудовуваних систем

[

ред.

|

ред. код

]

Ingenic

JZ4725 ? приклад SOC, базовано? на MIPS

Ingenic

JZ4725 ? приклад SOC, базовано? на MIPS

У 1990-т? роки, MIPS-арх?тектура була широко поширена на ринку

вбудовуваних систем

: для мереж, телекомун?кац?й, в?део ?гор, ?грових консолей, принтер?в, цифрових приставок, цифрових телев?зор?в,

xDSL

? кабельних модем?в, а також кишенькових комп'ютер?в.

Низьке енергоспоживання ? температурн? характеристики вбудованих MIPS-арх?тектур, широк? можливост? внутр?шн?х функц?й роблять цей м?кропроцесор ун?версальним для багатьох пристро?в.

Синтезован? ядра для ринку вбудованих систем

[

ред.

|

ред. код

]

В останн? роки б?льш?сть технолог?й, що використовуються в р?зних покол?ннях MIPS, запропонован? у вигляд?

IP-ядер

(стандартних блок?в) для вбудованих реал?зац?й процесора. Б?льше того, запропонован? обидва типи ядер ? заснован? на 32 ? 64 б?тах, в?дом? як 4 K ? 6 K.

Так? ядра можуть по?днуватися з ?ншими структурними елементами, такими як

FPU

, системами

SIMD

, р?зними пристроями введення / виводу ? т. д.

Колись комерц?йно усп?шн? ядра MIPS, ? в даний час знайшли споживче та промислове застосування. Ц? ядра можна знайти в нових маршрутизаторах

Cisco

,

Linksys

та

MikroTik

, кабельних ?

ADSL

модемах,

смарт-карта

х, механ?змах лазерних принтер?в, цифрових приставках, роботах, кишенькових комп'ютерах, Sony PlayStation 2 ? Sony PlayStation Portable. Тим не менш, в додатках моб?льних телефон?в ? PDA MIPS не вдалося зм?стити м?цно сталу там конкуруючу

ARM

-арх?тектуру.

Процесори п?д управл?нням MIPS включають в себе:

IDT

RC32438;

ATI

Xilleon;

Alchemy Au1000, 1100, 1200

;

Broadcom

Sentry5; RMI XLR7xx, Cavium Octeon CN30xx, CN31xx, CN36xx, CN38xx ? CN5xxx;

Infineon Technologies

EasyPort, Amazon, Danube, ADM5120, WildPass, INCA-IP, INCA-IP2;

Microchip Technology

PIC32

,

NEC

EMMA та EMMA2,

NEC

VR4181A, VR4121, VR4122, VR4181A, VR5432, VR5500; Oak Technologies Generation; PMC-Sierra RM11200 ; QuickLogic QuickMIPS ESP;

Toshiba

Donau,

Toshiba

TMPR492x, TX4925, TX9956, TX7901.

Суперкомп'ютери MIPS

[

ред.

|

ред. код

]

Одним з найц?кав?ших застосувань арх?тектури MIPS ? ?х використання в багатопроцесорних обчислювальних суперкомп'ютерах. На початку 1990-х компан?я Silicon Graphics (

SGI

) перенаправила св?й б?знес з граф?чних терм?нал?в на ринок високопродуктивного обчислення. Усп?х перших спроб компан?? в област? серверних систем (а саме, сер?я Challenge, заснована на R4400, R8000 ? R10000) мотивував SGI створити набагато потужн?шу систему. Використання R10000 дозволило компан?? спроектувати систему Origin 2000, в к?нцевому рахунку розширювану до 1024 ЦП, використовуючи власну м?жсистемних зв'язк?в cc-NUMA (NUMAlink). П?зн?ше Origin 2000 породила нову систему ? Origin 3000, що вийшла з тими ж максимальними 1024 ЦП, але використала в розробц? м?кросхеми R14000 та R16000 з частотою до 700 МГц. Проте, в 2005 роц?, коли SGI прийняла стратег?чне р?шення про перех?д на арх?тектуру

Intel

IA-64, суперкомп'ютери, базован? на MIPS були знят? з виробництва.

У 2007 роц? корпорац?я SiCortex представила новий багатопроцесорний персональний суперкомп'ютер, заснований на арх?тектур? MIPS. У його розробку лягли MIPS64 ? високопродуктивна м?жсистемна зв'язок з використанням тополог?? граф?в Кауца (

англ.

Kautz graph

). Дана система ? гранично ефективно? та обчислювально потужною. ?? ун?кальний аспект ? багатоядерний вузол обробки, ?нтегруючий ш?сть ядер MIPS64, комутатор контролера пам'ят?, м?жсистемних зв'язк?в механ?зм?в прямого доступу до пам'ят?, локальну мережу з пропускною здатн?стю 1 Гб?т ?

PCI Express

контролери. ? все це на одному кристал?, який спожива? 10 Вт енерг??, але викону? максимум 6 м?льярд?в операц?й з рухомою комою в секунду. Найпотужн?ша конф?гурац?я такого суперкомп'ютера ? верс?я SC5832, що склада?ться з 972 вузл?в (всього 5832 ядер MIPS64) ? викону? 8 200 000 000 000 операц?й з плаваючою крапкою в секунду.

Loongson поверта? до персонал?зац??

[

ред.

|

ред. код

]

Компан?я Loongson, в над?? об?йти патент MIPS, випустила свою арх?тектуру, яка була повн?стю схожа з розробкою MIPS Technologies ? п?дтримувалася ОС

Linux

. Через те, що виробництво процесор?в Loongson було дешевшим, MIPS отримали можлив?сть в?дродитися на ринку персональних комп'ютер?в в особ? Loongson. Надал? Loongson купили л?ценз?ю на MIPS.

Процесори арх?тектури MIPS також використовуються в

нетбуках

компан?й iUnika, Bestlink, Lemote ? Golden Delicious Computers.

MIPS IV

? це четверте покол?ння арх?тектури, явля? собою розширену верс?ю

MIPS III

? сум?сний з ус?ма ?снуючими моделями MIPS. Перший випуск MIPS IV був представлений в 1994 роц? п?д назвою

R8000

.

MIPS IV включив в себе:

- Проста адресац?я рег?стр + рег?стр для завантаження ? збер?гання чисел з рухомою комою

- Операц?? FMA ? FMS з одинарною ? подв?йною точн?стю для чисел з рухомою комою

- Команди умовного переходу для ц?лих чисел ? для чисел з рухомою комою

- Додатков? умовн? б?ти в рег?стр? контролю та стану числа з рухомою комою: в ц?лому 8 б?т?в.

MIPS V

? п'ята верс?я арх?тектури, була представлена 21 жовтня 1996 року на Форум? м?кропроцесор?в 1996. Ця модель була розроблена для того, щоб п?двищити продуктивн?сть граф?чних

3D

-додатк?в. В середин? 1990-х велика частина не вбудованих м?кропроцесор?в MIPS припадала на граф?чн? терм?нали в?д

SGI

. Розробка MIPS V була доповнена ц?лочисельними мультимед?йними розширеннями MDMX (MIPS Digital Media Extensions), як? були представлен? в той же день, що ? MIPS V.

Реал?зац?? MIPS V так н?коли ? не були впроваджен?. У 1997 роц? SGI представила м?кропроцесори п?д назвами ≪H1≫ (≪Beast≫) ? ≪H2≫ (≪Capitan≫), як? повинн? були бути проведен? в 1999 роц?. Але незабаром ?х об'?днали, ? в к?нцевому п?дсумку в 1998 роц? ц? проекти були скасован?.

В MIPS V був доданий новий тип даних ? PS (pair-single), який явля? собою два числа з рухомою комою подв?йно? точност? (32-б?тн?), що збер?гаються в 64-б?тному рег?стр? з рухомою комою. Щоб працювати з цим типом даних в режим?

SIMD

, були додан? р?зн? вар?анти арифметичних, пор?вняльних операц?й над числами з плаваючою точкою, а також команда умовного переходу. З'явилися нов? ?нструкц?? для завантаження, реконф?гурац?? ? перетворення PS-даних. Це перша арх?тектура, зум?ла реал?зувати обробку чисел з плаваючою точкою в

SIMD

-режим? з наявними ресурсами.

Родина процесор?в з арх?тектурою MIPS

[

ред.

|

ред. код

]

Першим комерц?йним м?кропроцесором з арх?тектурою MIPS був м?кропроцесор R2000, представлений в 1985 роц?. У ньому були реал?зован? операц?? множення ? д?лення, як? виконувалися за к?лька такт?в. Пристр?й множення ? д?лення не було т?сно ?нтегровано в ядро процесора, хоча й розм?щувалось на тому ж кристал?; з ц??? причини система команд розширена ?нструкц?ями для завантаження результат?в множення ? д?лення в рег?стри загального призначення, ц? ?нструкц?? блокували конве?р.

М?кропроцесор R2000 м?г бути завантажений як в режим? big-endian, так ? в режим? little-endian, м?стив тридцять два 32-розрядних рег?стра загального призначення. Под?бно процесорам AMD 29000 ?

Alpha

м?кропроцесор R2000 не мав окремого рег?стра прапор?в умов, так як розробники порахували його потенц?йним ≪вузьким м?сцем≫. Сл?д зазначити, що л?чильник команд безпосередньо недоступний.

М?кропроцесор R2000 п?дтримував п?дключення до чотирьох сп?впроцесор?в, один з яких ? вбудованим ? забезпечу? роботу з винятками, а також управл?ння пам'яттю (MMU). У раз? необх?дност? як ще один сп?впроцесор можна було п?дключити м?кросхему R2010, арифметичний сп?впроцесор, який м?стив тридцять два 32-розрядних рег?стра, як? можна було використовувати як ш?стнадцять 64-розрядних рег?стр?в для роботи з числами подв?йно? точност?.

Наступним в с?мейств? став R3000, який з'явився в 1988 роц?. В?н м?стив кеш-пам'ять даних об'?мом 64 КБ (R2000 ? 32 КБ). Кр?м того, R3000 забезпечував когерентн?сть кеш-пам'ят? при робот? в мультипроцесорних конф?гурац?ях. Незважаючи на те, що в п?дтримц? мультипроцессорности R3000 ? ряд недол?к?в, на баз? R3000 було створено дек?лька працездатних багатопроцесорних систем. Як ? для R2000, для R3000 був створений арифметичний сп?впроцесор у вигляд? окремо? СБИС: R3010. М?кропроцесор R3000 став першим комерц?йно усп?шним процесором з арх?тектурою MIPS, було виготовлено б?льше м?льйона процесор?в. Прискорена верс?я R3000, що працю? на тактов?й частот? 40 МГц, названа R3000A, досягла продуктивност? в 32 VUPs (VAX Unit of Performance). Подальший розвиток R3000A, м?кропроцесор R3051, що працю? на частот? 33,8688 МГц був використаний в ?гров?й приставц? Sony PlayStation. ?нш? виробники також представили процесори, сум?сн? з R3000A: в Performance Semiconductor був розроблений R3400, в той час як компан?я IDT створила R3500, обидва згаданих процесора мали в ?нтегрований математичний сп?впроцесор R3010. Першою системою на кристал?, що використову? процесор з арх?тектурою MIPS, стала розробка R3900 ф?рми Toshiba; дана м?кросхема використовувалася в портативному комп'ютер?, який працював п?д управл?нням Windows CE. Був розроблений рад?ац?йно-ст?йкий вар?ант R3000 з ?нтегрованим R3010, призначений для застосування в косм?чних апаратах, який отримав назву Mongoose-V.

Сер?я R4000, випущена в 1991 роц?, розширила процесори MIPS до 64 б?т?в. (MIPS Technology була першою компан??ю випустила процесори з 64-б?тово? арх?тектурою)

R4000 склада?ться з 1300000 транзистор?в, ма? вбудований кеш даних ? кеш ?нструкц?й (обидва по 8 Кб). У цьому процесор? зовн?шня тактова частота 50 МГц подвою?ться, а внутр?шня тактова частота становить 100 МГц. Процесор R4400 виконаний на основ? R4000, склада?ться з 2200000 транзистор?в, ма? вбудований кеш даних ? кеш ?нструкц?й (обидва по 16 Кб), а внутр?шня тактова частота становить 150 МГц. Наб?р команд цих процесор?в (специф?кац?я MIPS II) було розширено командами завантаження ? записи 64-розрядних чисел з плаваючою точкою, командами обчислення квадратного кореня з одинарною ? подв?йною точн?стю, командами умовних переривань, а також атомарними операц?ями, необх?дними для п?дтримки мультипроцесорних конф?гурац?й. В процесорах R4000 ? R4400 реал?зован? 64-б?тов? шини даних ? 64-б?тов? рег?стри.

MIPS, тепер ? в?дд?лом SGI п?д назвою MTI, розробив недорог? процесори R4200, що послужили основою для майбутн?х (ще б?льш дешевих) R4300i. Пох?дна цього процесора, NEC VR4300, використовувалася в ?грових консолях Nintendo 64.

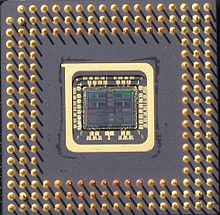

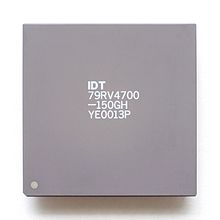

нижня сторона R4700 Orion, на як?й видно кремн??вий чип, виготовлений

IDT

? спроектований Quantum Effect Devices

нижня сторона R4700 Orion, на як?й видно кремн??вий чип, виготовлений

IDT

? спроектований Quantum Effect Devices

лицьова сторона R4700 Orion

лицьова сторона R4700 Orion

Quantum Effect Devices (QED), самост?йна компан?я, заснована розробниками MIPS, розробила сер?ю процесор?в R4600 Orion, R4700 Orion, R4650 ? R5000.

Якщо в R4000 зб?льшили тактову частоту, але пожертвували к?льк?стю кеш-пам'ят?, то QED прид?лили велику увагу ? ?мност? кеш-пам'ят? (доступ до яко? можна отримати всього за 2 цикли), ? ефективному використанню поверхн? кристала. Процесори R4600 ? R4700 використовувалися в недорогих верс?ях робочо? станц?? SGI Indy, а також у перших маршрутизаторах Cisco (заснованих на MIPS), наприклад, сер?? 36х0 ? 7х00. М?кропроцесор R4650 застосовувався в телев?з?йних приставках WebTV (нин? ? Microsoft TV). У процесор? R5000 FPU диспетчеризац?я операц?й з плаваючою точкою (одинарно? точност?) була гнучк?шою, н?ж в R4000, ?, внасл?док цього, робоч? станц?? SGI Indys, базован? на R5000 в?др?знялися кращою граф?чною продуктивн?стю, н?ж R4400 з такою ж тактовою швидк?стю ? граф?чним апаратним пристро?м. Щоб п?дкреслити пол?пшення п?сля об'?днання R5000 ? старо? граф?чно? плати, SGI дала ?й нову назву. Трохи п?зн?ше QED розробили с?мейство процесор?в RM7000 ? RM9000 для ринку мереж ? лазерних принтер?в. У серпн? 2000 року компан?я QED була придбана виробником нап?впров?дник?в PMC-Sierra, ? остання продовжила ?нвестування MIPS-арх?тектур. Процесор RM7000 включав в себе 256 Кб вбудовано? кеш-пам'ят? 2-го р?вня ? контролер для додатково? кеш-пам'ят? 3го р?вня. Були створен? процесори RM9xx0 ? с?мейство SOC-пристро?в, в як? включен? так? перифер?йн? складов? (на п?вн?чному мосту) як: контролер пам'ят?, PCI-контролер, контролер Ethernet, а також швидк? пристро? введення-виведення (наприклад, високопродуктивна шина типу HyperTransport).

R8000 (представлений в 1994 роц?) був першою суперскалярно? арх?тектурою MIPS, здатно? зд?йснювати 2 ц?лочисельн? ?нструкц?? (або з плаваючою точкою) ? 2 ?нструкц?? звернення до пам'ят? за один цикл. Дана розробка використовувала 6 схем: пристр?й для ц?лочислових команд (16 Кб ? команди ? 16 Кб ? кеш даних), для команд з плаваючою точкою, три вторинних дескриптора кеш-пам'ят? ОЗУ (два для вторинного доступу до кеш-пам'ят? + один для в?дстеження шини), а також кеш-контролер ASIC. Арх?тектура ма? два повн?стю конвейер?зовать пристрою множення-складання (з подв?йною точн?стю), як? можуть передавати пот?к даних в 4 Мб внекр?стального вторинного кешу. В середин? 1990-х процесори R8000 запустили SGI сервери POWER Challenge, а п?зн?ше стали доступн? на робочих станц?ях POWER Indigo2. Хоча продуктивн?сть цього FPU ? була найб?льш п?дходящою для наукових сп?вроб?тник?в, обмежен?сть його целочисленной продуктивност? ? висока ц?на не змогли залучити б?льш?сть користувач?в, тому R8000 був на ринку всього р?к, ? нав?ть зараз його навряд чи можна знайти.

У 1995 роц? був випущений R10000. Цей процесор в однокристальному виконанн?, працював з б?льш високою тактовою частотою, н?ж R8000, а також включав в себе об'?мну (32 КБ) первинну кеш-пам'ять даних ? команд. Кр?м того, в?н був суперскалярних, але це головне нововведення було несправне. Але нав?ть з прост?шим FPU, значно зб?льшена продуктивн?сть ц?лочисельний обчислень, нижча ц?на та висока щ?льн?сть запису зробили R10000 кращим для б?льшост? користувач?в.

Ус? п?зн?ш? проекти були заснован? на ядр? R10000. В R12000 був використаний 0,25 м?кронний технолог?чний процес з метою зменшити чип ? досягти б?льшо? тактовою швидкост?. Виправлений R14000 мав вищу тактову частоту на додаток з п?дтримкою DDR SRAM для внекр?стальной кеш-пам'ят?. Сл?дом були випущен? R16000 ? R16000A, тактова частота яких була також зб?льшена; в них була вбудована додаткова кеш-пам'ять першого р?вня, а ?х виробництво вимагало др?бн?ших кристал?в, н?ж ран?ше.

Серед ?нших представник?в с?мейства MIPS ? R6000, ЕСЛ-реал?зац?я, виконана компан??ю Bipolar Integrated Technology. R6000 в?дноситься до покол?ння процесор?в MIPS II. Його TLB ? пристр?й кеш-пам'ят? значно в?др?зняються в?д ?нших представник?в даного с?мейства. R6000 не прин?с об?цяно? вигоди, ?, хоча був визнаний деякою м?рою корисним для комп'ютер?в Control Data, в?н митт?во зник з основного ринку.

М?кропроцесори MIPS

| Модель

|

Частота (МГц)

|

Р?к

|

Технолог?я розробки (μm)

|

Транзистори (млн.)

|

Розм?р кристала (мм²)

|

Число висновк?в

|

Потужн?сть (Вт)

|

Напруга (В)

|

Кеш даних (КБ)

|

Кеш ?нструкц?й (КБ)

|

Кеш 2го р?вня

|

Кеш 3го р?вня

|

| R2000

|

8-16.67

|

1985

|

2,0

|

0,11

|

?

|

?

|

?

|

?

|

32

|

64

|

Н?

|

НЕМА?

|

| R3000

|

12-40

|

1988

|

1,2

|

0,11

|

66,12

|

145

|

4

|

?

|

64

|

64

|

0-256 Кб Зовн?шня

|

НЕМА?

|

| R4000

|

100

|

1991

|

0,8

|

1,35

|

213

|

179

|

15

|

5

|

8

|

8

|

1 Мб Зовн?шня

|

НЕМА?

|

| R4400

|

100-250

|

1992

|

0,6

|

2,3

|

186

|

179

|

15

|

5

|

16

|

16

|

1-4 Мб Зовн?шня

|

НЕМА?

|

| R4600

|

100-133

|

1994

|

0,64

|

2,2

|

77

|

179

|

4,6

|

5

|

16

|

16

|

512 Кб Зовн?шня

|

НЕМА?

|

| R4700

|

133

|

1996

|

?

|

?

|

?

|

179

|

?

|

?

|

16

|

16

|

Зовн?шня

|

НЕМА?

|

| R5000

|

150-200

|

1996

|

0,35

|

3,7

|

84

|

223

|

10

|

3,3

|

32

|

32

|

1 Мб Зовн?шня

|

НЕМА?

|

| R8000

|

75-90

|

1994

|

0,7

|

2,6

|

299

|

591 +591

|

30

|

3,3

|

16

|

16

|

4 Мб Зовн?шня

|

НЕМА?

|

| R10000

|

150-250

|

1996

|

0,35, 0,25

|

6,7

|

299

|

599

|

30

|

3,3

|

32

|

32

|

512 Кб-16 Мб Зовн?шня

|

НЕМА?

|

| R12000

|

270-400

|

1998

|

0,25, 0,18

|

6,9

|

204

|

600

|

20

|

4

|

32

|

32

|

512 Кб-16 Мб Зовн?шня

|

НЕМА?

|

| RM7000

|

250-600

|

1998

|

0,25, 0,18, 0,13

|

18

|

91

|

304

|

10, 6, 3

|

3,3, 2,5, 1,5

|

16

|

16

|

256 Кб Внутр?шня

|

1 Мб Зовн?шня

|

| R14000

|

500-600

|

2001

|

0,13

|

7,2

|

204

|

527

|

17

|

?

|

32

|

32

|

512 Кб-16 Мб Зовн?шня

|

НЕМА?

|

| R16000

|

700-1000

|

2002

|

0,11

|

?

|

?

|

?

|

20

|

?

|

64

|

64

|

512 Кб-16 Мб Зовн?шня

|

НЕМА?

|

| R24K

|

750 +

|

2003

|

65 nm

|

?

|

0.83

|

?

|

?

|

?

|

64

|

64

|

4-16 Мб Зовн?шня

|

НЕМА?

|

Формат ?нструкц?й MIPS I

[

ред.

|

ред. код

]

?нструкц?? под?ляються на три типи: R, I ? J. Кожна ?нструкц?я почина?ться з 6-б?тного коду. На додаток до коду, ?нструкц?? R-типу визначають три рег?стра, область розм?ру зсуву рег?стра, ? область функц??; ?нструкц?? I-типу визначають два рег?стри ? безпосередн? значення; ?нструкц?? J-типу сл?дують коду операц?? з 26-б?товим кроком.

Мова асемблера MIPS

[

ред.

|

ред. код

]

Дан? ?нструкц?? мови асемблера мають пряму апаратну реал?зац?ю, на в?дм?ну в?д псевдо?нструкц?й, як? перед складанням транслюються в справжн? складов? ?нструкц??.

- Дал?, ре?стров? л?тери d, t, ? s будуть позначати покажчики на номери ? ?мена рег?стр?в.

- C познача? константу.

- Ус? наступн? команди ? власними.

- Вс? коди операц?й ? функц?й представлен? в ш?стнадцятков?й систем? числення.

- Наб?р ?нструкц?й MIPS32 ?дентиф?ку?, що число без знака, яка бере участь у складанн? або вирахуванн?, некоректно. Р?зницею м?ж форматами числа з? знаком ? без ? не зб?льшення довжини операнд?в (або ?? зменшення), а здатн?сть розп?знавати, чи було переривання та в раз? переповнення, або ж переривання було про?гноровано. Операнд константа, у в?дпов?дн?сть з цими ?нструкц?ями, завжди повинен мати знак.

Ц?лочисельн? операц??

[

ред.

|

ред. код

]

MIPS ма? 32 рег?стра для ц?лочисельних операц?й. Для виконання арифметичних обчислень дан? повинн? перебувати в рег?страх. Рег?стр $ 0 завжди збер?га? 0, а рег?стр $ 1 резерву?ться для зб?рки (для збер?гання псевдо?нструкц?й ? великих констант).

Операц?? над числами з плаваючою точкою

[

ред.

|

ред. код

]

MIPS ма? 32 рег?стра з плаваючою крапкою. Рег?стри з'?днан? по 2 для подв?йно? точност? обчислень. Рег?стри з непарними номерами не можуть бути використан? для арифметичних операц?й або розгалуження, вони можуть лише частково вказувати подв?йну точн?сть в пар? рег?стр?в.

Ц? ?нструкц?? приймаються мовою асемблера MIPS, проте вони не ? реальними. Асемблер переводить ?х в посл?довност? справжн?х ?нструкц?й.

К?лька ?нших важливих ?нструкц?й

[

ред.

|

ред. код

]

- NOP (без операц??) (машинний код 0x00000000, ?нтерпрету?ться в процесором як sll $ 0, $ 0, 0)

- Break (розриви програми, використову?ться в?дладниками)

- Системний виклик (використову?ться для системних виклик?в операц?йно? системи)

Використання рег?стра транслювання

[

ред.

|

ред. код

]

Апаратна арх?тектура визнача? наступн? критер??:

- Рег?стр загального призначення $ 0 завжди поверта? значення 0.

- Рег?стр загального призначення $ 31 використову?ться як рег?стра-посилання для команд переходу ? зв'язку.

- HI ? LO використовуються для доступу до результат?в множення / д?лення, доступ до яких зд?йсню?ться командами mfhi (move from high) ? mflo (move from low).

Це ?дин? обмеження, як? апаратна арх?тектура наклада? на використання рег?стр?в загального призначення.

Р?зн? пристро? MIPS реал?зовують спец?альн? угоди про виклики, як? обмежують використання рег?стр?в. Угоди про виклики повн?стю п?дтримуються комплексом ПО, але не потр?бн? апаратним забезпеченням.

Захищен? рег?стри (за угодою) не можуть бути зм?нен? викликом системи або процедури (функц??). Наприклад, $ s-рег?стри повинн? бути збережен? в стец? процедурою, яка збира?ться ними скористатися; до $ sp ? $ fp-рег?стр?в прирощу?ться константи, а п?сля зак?нчення процедури рег?стри знову зменшуються. Протилежним прикладом служить рег?стр $ ra, який автоматично зм?ню?ться при його виклику будь функц??ю. $ T-рег?стри повинн? збер?гатися програмою перед викликом будь-яко? процедури (якщо програм? потр?бн? дан?, отриман? п?сля виклику).

Серед

Open Virtual Platforms

?сну? безкоштовний емулятор OVP-sim, доступний для некомерц?йного використання, який явля? собою б?бл?отеку моделей процесор?в ? платформ, а також програмних ?нтерфейс?в, що дозволяють користувачев? проектувати власн? модел?. Б?бл?отека моделей ? в?дкритим ресурсом, написаному мовою С, ? включа? в себе ядра MIPS 4K, 24K ? 34K. Дан? модел? створен? ? п?дтримуються компан??ю Imperas, яка у сп?впрац? з

MIPS Technologies

протестувала емулятор ? в?дзначила його знаком MIPS-Verified. Зразки платформ, заснованих на MIPS включають в себе як апаратне забезпечення, так ? платформи для завантаження немодиф?кованих дв?йкових образ?в Linux. Так? платформи-емулятори ефективн? для навчання, а також доступн?, безкоштовн? ? прост? у використанн?. OVPsim розроблений ? п?дтримуваний Imperas працю? з високою швидк?стю (сотн? м?льйон?в ?нструкц?й на секунду), ? може бути використаний для опису багатоядерних арх?тектур.

?сну? в?льно доступний емулятор MIPS32 (ранн? верс?? могли ?м?тувати т?льки R2000/R3000), випущений п?д назвою SPIM ? призначений для використання в навчанн?. EduMIPS64 ? це м?жплатформовий граф?чний емулятор процесора MIPS64, написаний мовою

Java

з використанням граф?чно? б?бл?отеки Swing. В?н п?дтриму? множину команд MIPS64

ISA

? дозволя? користувачев? наочно побачити, що в?дбува?ться в конве?р?, коли ЦП викону? програму мовою асемблера. Проект ма? строго осв?тн? ц?л? ? широко використову?ться на деяких курсах комп'ютерно? арх?тектури в усьому св?т?.

Ще один GUI-емулятор процесор?в MIPS ? це MARS, теж розроблений в осв?тн?х ц?лях, особливо ефективний разом з книгою Геннесс?

Computer Organization and Design

.

Б?льш просунут? верс?? безкоштовних емулятор?в ? Gxemul (ран?ше в?дом? як проекти mips64emul), а також проекти

QEMU

. Вони ?м?тують р?зн? модел? м?кропроцесор?в MIPS III ? MIPS IV (як доповнення до комп'ютерних систем, що ?х використовують).

Комерц?йн? розробки емулятор?в доступн? в основному для вбудованого використання процесор?в MIPS, наприклад, Virtutech Simics (MIPS 4Kc ? 5Kc, PMC RM9000, QED RM7000), VaST Systems (R3000, R4000), ? CoWare (MIPS4KE, MIPS24K, MIPS25Kf ? MIPS34K).

Список процесор?в на баз? арх?тектури MIPS

[

ред.

|

ред. код

]

- Alchemy

Au1000, 1100, 1200

- Atheros

AR23xx, AR52xx, AR71xx, AR72xx

- ATI

Xilleon

- Broadcom

Sentry5

- IDT

RC32438

- Infineon Technologies

EasyPort, Amazon, Danube, ADM5120, WildPass, INCA-IP, INCA-IP2

- Ingenic

JZ47xx

- Lemote

Loongson I

, Loongson II, Loongson III

[3]

- Microchip Technology

PIC32

- Mongoose-V

- NEC

EMMA and EMMA2, NEC VR4181A, VR4121, VR4122, VR4181A, VR5432, VR5500

- Oak Technologies

Generation

- PMC-Sierra

RM11200

- Realtek

RTD1055, RTD1185, RTD1186

[4]

- Sigma Designs

SMP8640, SMP8650, SMP8910

[5]

- QuickLogic

QuickMIPS ESP

- RMI

XLR7xx, Cavium Octeon CN30xx, CN31xx, CN36xx, CN38xx и CN5xxx

- Toshiba

Donau, Toshiba TMPR492x, TX4925, TX9956, TX7901.