Si ce bandeau n'est plus pertinent, retirez-le. Cliquez ici pour en savoir plus.

Si ce bandeau n'est plus pertinent, retirez-le. Cliquez ici pour en savoir plus.

Un signal d'horloge est typiquement un

signal carre

.

Un signal d'horloge est typiquement un

signal carre

.

Un signal d'horloge est produit par un

generateur d'horloge

, ici dans un

ordinateur de bureau

, constitue d'une puce (a droite) et d'un resonateur (a gauche).

Un signal d'horloge est produit par un

generateur d'horloge

, ici dans un

ordinateur de bureau

, constitue d'une puce (a droite) et d'un resonateur (a gauche).

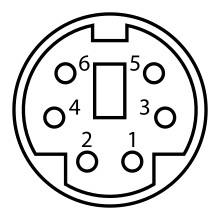

Connecteur PS/2

: le signal d'horloge se trouve sur les broches 5 et 6, respectivement pour la souris et le clavier.

Connecteur PS/2

: le signal d'horloge se trouve sur les broches 5 et 6, respectivement pour la souris et le clavier.

Un

signal d’horloge

est, en

electronique

, et particulierement en

electronique numerique

, un

signal electrique

oscillant

qui rythme les actions d'un

circuit

. Sa

periode

est appelee

cycle d’horloge

[

1

]

.

A chaque cycle d'horloge, des calculs peuvent etre effectues en utilisant les sorties de

bascules

. L'horloge permet d'assurer que les donnees sont valides au cycle d'horloge suivant, c'est-a-dire que les calculs sont termines et les resultats stabilises. Meme certains

filtres

, comme les

circuits a capacites commutees

, doivent etre cadences par un circuit d'horloge

[

2

]

. La duree du cycle doit donc etre choisie en fonction du

temps de reponse

des

portes logiques

.

exemple de signal d'horloge

exemple de signal d'horloge

On considere generalement qu'un circuit est d'autant plus rapide que la frequence du signal d'horloge qui le synchronise est elevee. Cependant, l’

overclocking

, c'est-a-dire l'augmentation de la

frequence d'horloge

, entraine une augmentation de la consommation electrique et, par

effet ohm

, de la temperature. Augmenter la tension ou refroidir le circuit sont donc necessaires pour augmenter la vitesse de commutation des transistors, et donc augmenter la frequence d'horloge ; mais a partir d'une certaine frequence, le circuit ≪ decroche ≫ : certains signaux ne sont pas stabilises a l'arrivee d'une impulsion, ce qui conduit a des erreurs que le

controle de checksum

ne suffit plus a reparer.

Pour accelerer encore le circuit, on peut diminuer la taille des plus longs

circuits logiques

, par exemple en y ajoutant des etages de

bascules

intermediaires : ils s'executeront alors en plusieurs cycles, permettant d'augmenter la frequence et d’executer les autres calculs plus rapidement.

Dans le cas de

processeurs

, de nombreuses autres proprietes entrent en ligne de compte, comme le

parallelisme au niveau des instructions

, la

prediction de branchement

ou le temps d'acces a la memoire. La frequence d'horloge ne permet donc de comparer que des processeurs de conception proche.

Un des problemes recurrents pour les horloges est la variation de leur periode. Ce phenomene, appele

gigue d'horloge

, cause des problemes pour la fiabilite du circuit et complique la montee en frequence : une periode trop courte peut en effet activer les bascules avant que le resultat du circuit precedent ne soit disponible, ce qui oblige le concepteur a utiliser un cycle moyen suffisamment long pour que cela ne se produise pas.

L’horloge qui genere ce signal etant en general reliee a un tres grand nombre de bascules, elle possede un

fan-out

important, ce qui conduit a la conception d’un

arbre d’horloge

, et a l'insertion de repeteurs. On utilise des algorithmes specialises pour router ce circuit, de maniere a controler au mieux les differences de delais.

D'autres methodes ont ete etudiees pour reduire l'energie consommee par ce circuit et les differences de delais. On peut citer, par exemple, l'utilisation des proprietes de resonance des

circuits RLC

pour entretenir les oscillations

[

3

]

.

L'horloge peut representer une part importante de la consommation d'energie d'un circuit : les fronts d'horloge consomment de l'energie en chargeant et dechargeant les fils, et en activant les

bascules

qui y sont reliees. Pour reduire la consommation des circuits synchrones, on utilise le

clock gating

, qui consiste a couper l'horloge dans les parties inactives du circuit.

Meme si la plupart des circuits electroniques complexes sont synchronises par une horloge, il est possible d'en concevoir qui n'en possedent pas. On parle alors de

circuit asynchrone

. Inversement, on parle de circuits synchrones pour ceux utilisant un unique signal d'horloge.

- ↑

Lee Morgan, ≪

Comment caracteriser et resoudre les problemes de gigue sur les systemes embarques

≫, sur

Actutem

,

- ↑

Paul Horowitz et Winfield Hill,

The Art of Electronics

, Cambridge, GB, Cambridge University Press,

(

reimpr.

2e edition)

(

ISBN

0521370957

)

,

p.

282

- ↑

(en)

Rachel Courtland, ≪

Power-Saving Clock Scheme in New PCs

≫, sur

IEEE Spectrum

,

.